# arm

# SVE Enablement in RMM for Realms

Arunachalam Ganapathy 01 June 2023

© 2023 Arm

### Agenda

#### **Brief Introduction**

- Scalable Vector Extension (SVE)

- Realm Management Extension (RME)

- Realm Management Monitor (RMM)

#### SVE Support in RMM for Realms

- Existing support in RMM for FP/NEON

- SVE Requirements and Design goals

- SVE Support Lazy Enablement

- RMM SIMD abstraction layer

- RMM use of FPU at REL2

- SVE Hint bit handling

#### **Upstream Status**

- TF-RMM, tf-a-tests

- Related upcoming features: SME

# Scalable Vector Extension (SVE)

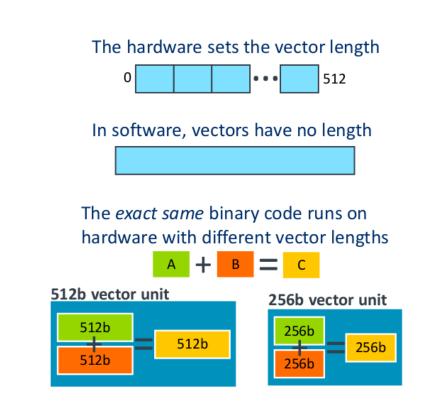

- -- Added in Armv8-A (from v8.2)

- -- Key Features:

- -- SIMD with larger and scalable vector length

- + Vector Length Agnostic (VLA)

- -- Per lane predication

- + Gather load and Scatter Store

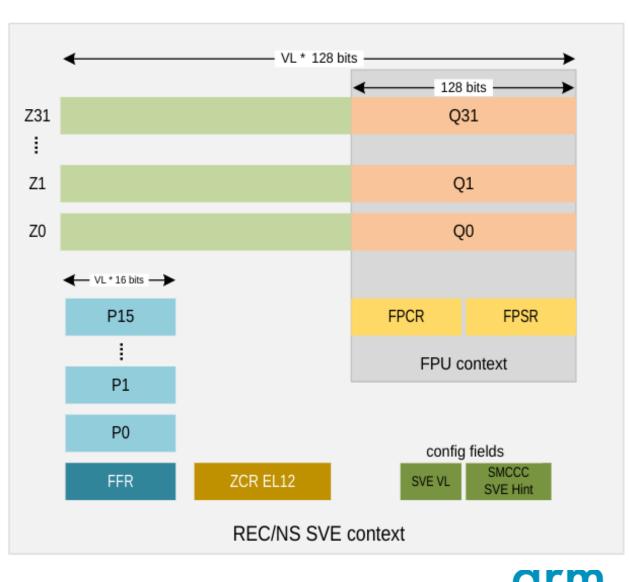

- -- Register state

- Vector registers Z[0-31]. Scalable from 128-2048 bits.

Shares the lower 128 bits with FP/NEON vector register.

- -- Predicate registers P[0-15]

- -- First Fault Register FFR

- -- Control Register

- -- ZCR\_ELx: Restricts Vector Length to current and lower ELs

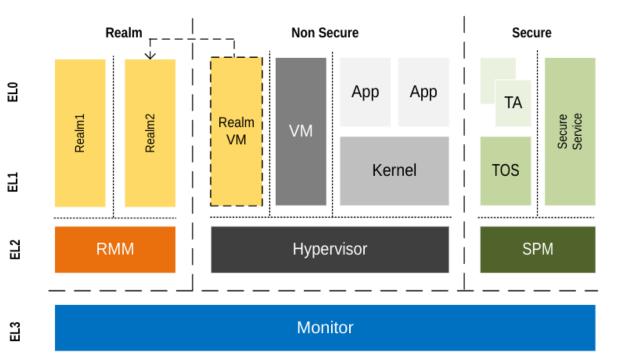

### Realm Management Extension (RME) and Realms

- RME added in Armv9-A (from v9.2)

- -- RME allows to do Confidential Compute on Arm

- -- Adds Root world, Realm world along with existing Nonsecure and Secure world

- --- Introduces Physical Address Space (PAS) for each world.

- Dynamically assign granule from one PAS to another PAS, using Granule Protection Table (GPT)

- -- Realm Management Monitor (RMM)

- Software component part of the system that implements Arm CCA

- -- Realms

- RME in H/W and RMM in S/W provides support for NS VMM (hypervisor) to create protected execution environment called Realms.

#### Introduction

- Scalable Vector Extension (SVE)

- Realm Management Extension (RME)

- Realm Management Monitor (RMM)

#### **SVE Support in RMM for Realms**

- Existing support in RMM for FP/NEON

- SVE Requirements and Design goals

- SVE Support Lazy Enablement

- RMM SIMD abstraction layer

- RMM use of FPU at REL2

- SVE Hint bit handling

#### **Upstream Status**

- TF-RMM, tf-a-tests

- Related upcoming features: SME

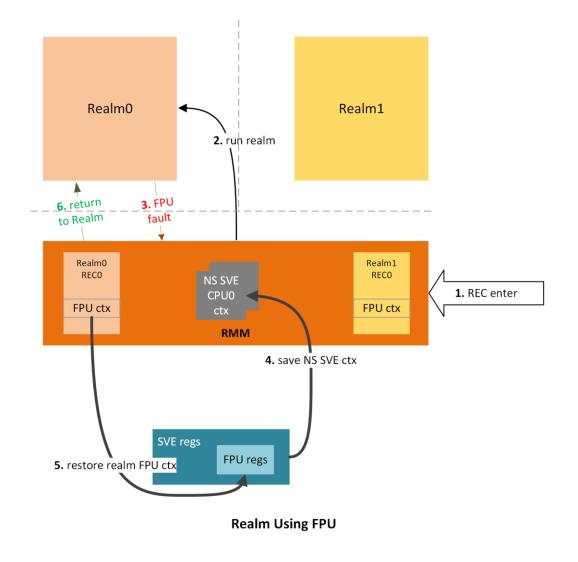

## Support in TF-RMM v0.2.0 for FPU/NEON

#### + FP/NEON support in Realms

- + FPU support for Realms

- -- Lazy enablement. REC runs with FPU traps enabled.

- Upon FPU exception, RMM restores REC state and REC continues execution.

- -- FPU state held in REC page

- -- Non Secure SVE state management

- Special config for RMM to use FPU at REL2

- Build flag RMM\_FPU\_USE\_AT\_REL2, OFF by default

- When set, mbedtls uses AdvSIMD (which requires FPU registers) at REL2 for attestation/measurement functionality.

- Needs crypto plugin in FVP

#### SVE support for Realms

#### **Requirements:**

- Support running multiple Realms with different vector length

- Handle FPU/SVE state, not leak/corrupt SVE Z/P registers b/w Realms and b/w Realm/NS world.

- Report H/W SVE status and max VL through RMM feature register 0

- Validate SVE flags, SVE VL on Realm creation. Propagate these flags to REC upon REC creation.

- Emulate sysregs read access to ID\_AA64PFR0\_EL1, ID\_AA64ZFR0\_EL1

- Support SVE hint bit (SMCCCv1.3)

## SVE support for Realms

| SVE in H/W | SVE enabled for Realms? | Notes                                                                                                                                                                                                                                                                                                       |

|------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | N/A                     | Access to SVE results in undefined abort                                                                                                                                                                                                                                                                    |

| 1          | 0                       | <ul> <li>Emulate ID register read for Realms <ul> <li>Clear SVE bits in ID_AA64PFR0_EL1</li> <li>Return 0 in ID_AA64ZFR0_EL1</li> </ul> </li> <li>Inject undefined abort when Realm access SVE registers/instructions</li> <li>Manage NS SVE state</li> <li>Continue with lazy enablement of FPU</li> </ul> |

| 1          | 1                       | <ul> <li>Manage NS SVE state</li> <li>Manage lazy enablement of SVE</li> <li>SVE VL for Realms configured by NS host</li> </ul>                                                                                                                                                                             |

### Realm creation with SVE

### SVE state in RMM

- -- RMI Feature Register 0

- --- SVE\_EN: flag set to 1 enables SVE

- -- SVE\_VL: can range from 0 to 15. (128 2048 bits vector length)

- -- NS Host queries this register and set the required values

- -- SVE Flags stored in realm data structure by RMM.

- AUX granules hold the SVE state (this encompasses FPU state as well)

- SVE state per REC is ~8700 bytes

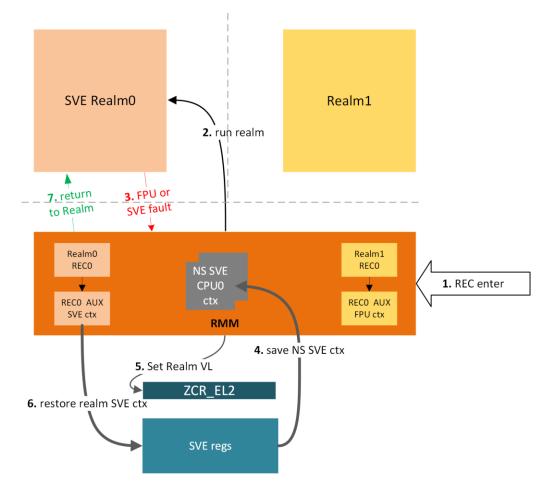

### SVE support - Lazy Enablement

- Handling REC SVE state

- Like FP/NEON, SVE also uses Lazy enablement. REC runs with SVE traps enabled

- -- Upon FPU or SVE exception, the whole SVE state of REC is restored after saving NS SVE state.

- -- Realm's SVE VL is programmed to ZCR\_EL2 before the running the realm.

- Handling NS SVE state

- While saving/restoring NS SVE state, ZCR\_EL2 is programmed to the max SVE VL limited by EL3 through ZCR\_EL3.

- RMM saves and restores NS ZCR\_EL2 register. RMM does not rely on EL3 to save and restore NS ZCR\_EL2 but expects this to be passthrough.

**Realm Using SVE**

#### **RMM SIMD abstraction layer**

- All FPU and SVE low level functions are abstracted under SIMD layer.

- Resides in lib/arch

- Currently SIMD type can be SIMD\_FPU or SIMD\_SVE, can be extended to add SIMD\_SME

- Provides APIs for RMM core to initialize, configure, save and restore any type of SIMD state

- Manages

- REC's SIMD state (could be FPU or SVE)

- NS SIMD state (could be FPU or SVE)

- RMM SIMD state (FPU only, when RMM\_FPU\_USE\_AT\_REL2=ON)

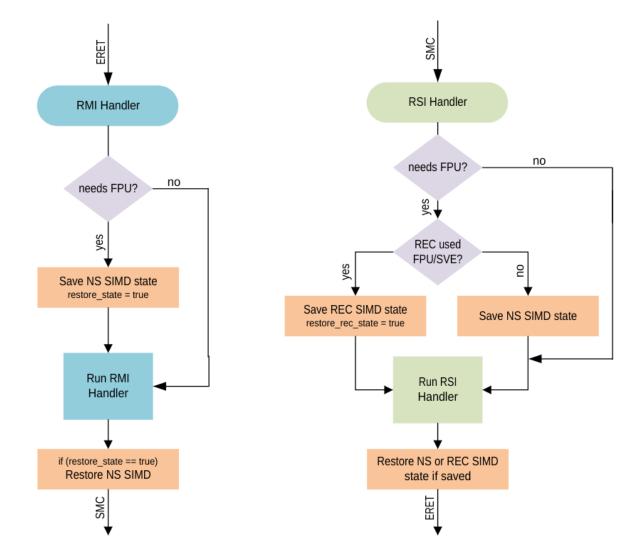

### RMM Use of FPU at REL2

- Build flag RMM\_FPU\_USE\_AT\_REL2=ON. mbedtls uses FPU in RMM (at REL2)

- RMI and RSI Handlers calls attestation layer

- RMI Handlers

- NS SIMD state is actively saved upon selected RMI handler that uses FPU

- RSI Handlers

- REC SIMD state is actively saved for selected RSI handler, if REC has used SIMD (FPU or SVE) else NS SIMD state is saved.

- FPU\_ALLOW()

- Macro enables use of FPU. Disable FPU traps at EL2

- Checks CPU live SIMD state is saved

FPU use at REL2 by RMI/RSI handlers

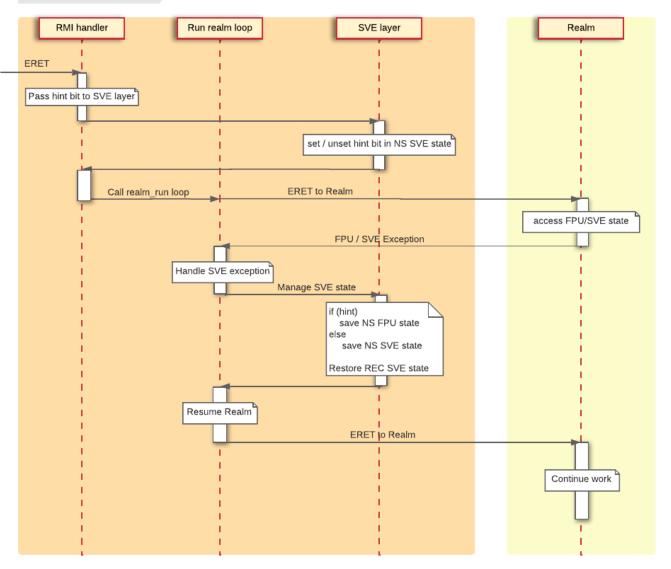

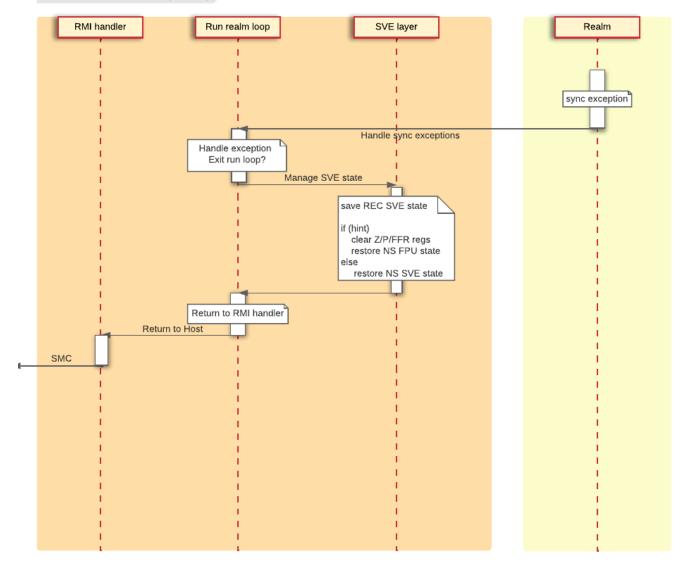

### SVE Hint bit handling in RMM (Planned)

Host Side SVE hint bit

### SVE Hint bit handling in RMM (Planned)

Host Side SVE hint bit (cont...)

#### Introduction

- Scalable Vector Extension (SVE)

- Realm Management Extension (RME)

- Realm Management Monitor (RMM)

#### **SVE Support in RMM for Realms**

- Requirements and Design Goals

- Existing support in RMM for FP/NEON

- SVE Support Lazy Enablement

- SIMD abstraction layer

- RMM using FPU at REL2

- SVE Hint bit handling

#### **Upstream Status**

- TF-RMM, tf-a-tests

- Related upcoming features: SME

### Upstream Status (v0.3.0)

#### • TF-RMM:

- Patches merged in tf-rmm-0.3.0 release.

- TF-RMM SVE support patchset

- tf-a-tests:

- Support added in TFTF framework for SVE tests in Realm payload

- Related upcoming features:

- RMM support to handle NS SME state

- RMM v1.0 specification does not cater for Realms to use SME

- Patches (in review) for <u>RMM SME support</u>

| FVP terminal_0                                                                                                                                                                                                                                                                                             |                |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| > Executing 'Check RMI reports proper SVE VL'<br>TEST COMPLETE                                                                                                                                                                                                                                             | Passed         |  |

| > Executing 'Create SVE Realm with invalid VL'<br>ERROR: host_rmi_realm_create() failed, rd=0x88c00000 ret=0x1<br>ERROR: host_realm_create() failed<br>TEST COMPLETE                                                                                                                                       | Passed         |  |

| > Executing 'Create SVE Realm and test ID registers'<br>INFO: Booting<br>Realm: reading ID registers: ID_AA64PFR0_EL1, ID_AA64ZFR0_EL1<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                              | Passed         |  |

| > Executing 'Create non SVE Realm and test ID registers'<br>INFO: Booting<br>Realm: reading ID registers: ID_AA64PFR0_EL1, ID_AA64ZFR0_EL1<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                          | Passed         |  |

| > Executing 'Create SVE Realm and check rdvl result'<br>INFO: Booting<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                                                                                               | Passed         |  |

| > Executing 'Create SVE Realm and probe all supported VLs'<br>INFO: Booting<br>INFO: Supported SVE vector length in bits (expected):<br>INFO: 128<br>INFO: 256<br>INFO: 512<br>INFO: 512<br>INFO: 128<br>INFO: 128<br>INFO: 512<br>INFO: 512<br>INFO: 512<br>INFO: 512<br>INFO: 512<br>INFO: TEST COMPLETE | Passed         |  |

| > Executing 'Check whether RMM preserves NS ZCR_EL2 register'<br>INFO: Booting<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                                                                                      | Passed         |  |

| > Executing 'Intermittently switch to Realm while doing NS SVE<br>INFO: Booting<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                                                                                     | ops'<br>Passed |  |

| > Executing 'Check if RMM does not leak Realm SVE vector regist<br>INFO: Booting<br>INFO: Powering off<br>TEST COMPLETE                                                                                                                                                                                    | ers'<br>Passed |  |

| +          | + |  |  |  |  |                  |            |

|------------|---|--|--|--|--|------------------|------------|

| ar         |   |  |  |  |  | Thank You        |            |

|            |   |  |  |  |  | + Danke          |            |

|            |   |  |  |  |  | Gracias          |            |

|            |   |  |  |  |  | + Grazie<br>谢谢   |            |

|            |   |  |  |  |  | ありがとう            |            |

|            |   |  |  |  |  | Asante           |            |

|            |   |  |  |  |  | → Merci<br>감사합니다 |            |

|            |   |  |  |  |  | धन्यवाद          |            |

|            |   |  |  |  |  | Kiitos           |            |

|            |   |  |  |  |  | شکرًا<br>۲۰ اهر  |            |

| © 2023 Arm |   |  |  |  |  | יתשדה +          | <b>m</b> + |