# arm

## Adding v8-R64 Support to TF-A

**TF-A Tech Forum**

Gary Morrison and Lauren Wehrmeister 1 July 2021

I © 2020 Arm Limited

#### What to do:

- What's v8-R64?

- v8-R64 architecture differences

- No-EL3

- MPU vs. MMU

- Secure-Mode Only

- No AArch32 support

- Why add v8-R64 support to v8-A firmware?

#### How to do it:

- The immediate assignment

- No-EL3 ramifications

- MPU ramifications

- No non-secure ramifications

- Loading runtime system and transfer of control

- Porting approach

- Review approach

## arm

### Armv8-R AArch64 Architecture ("v8-R64")

l © 2020 Arm Limited

#### What's v8-R64?

- Next generation of R-Class family: AArch64. Cortex-R82 is first implementation.

- R-Class cores are especially targeted toward *deterministic performance* (e.g., avoiding the unpredictable timing of table walks).

- Markets that have shown interest include Automotive and Computational Storage.

- The R-Class community is excited for all the reasons you'd expect:

- Vastly-increased address space

- Much-higher performance

- v8-R64 can support rich-OSes in addition to comparatively-spartan RTOSes.

- More information available here: <u>https://developer.arm.com/ip-products/processors/cortex-r/cortex-r82</u>

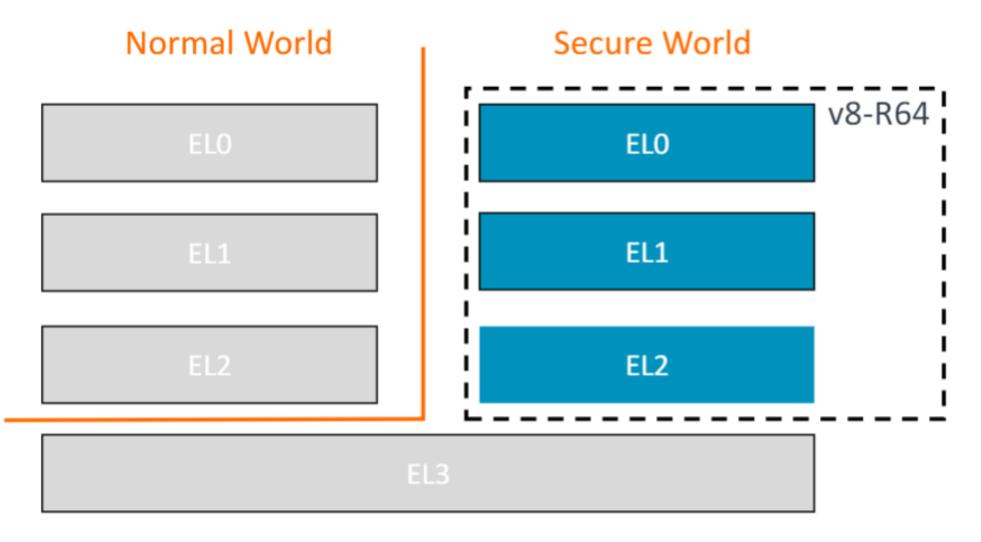

### v8-R64 Architecture Differences

Most basic differences compared to A-Class cores:

- No EL3.

- Everything is Secure.

- For Stage 2 translation, MPU only.

- For Stage-1 translation, MMU or MPU.

- No AArch32 support.

#### v8-R64 Architecture Differences

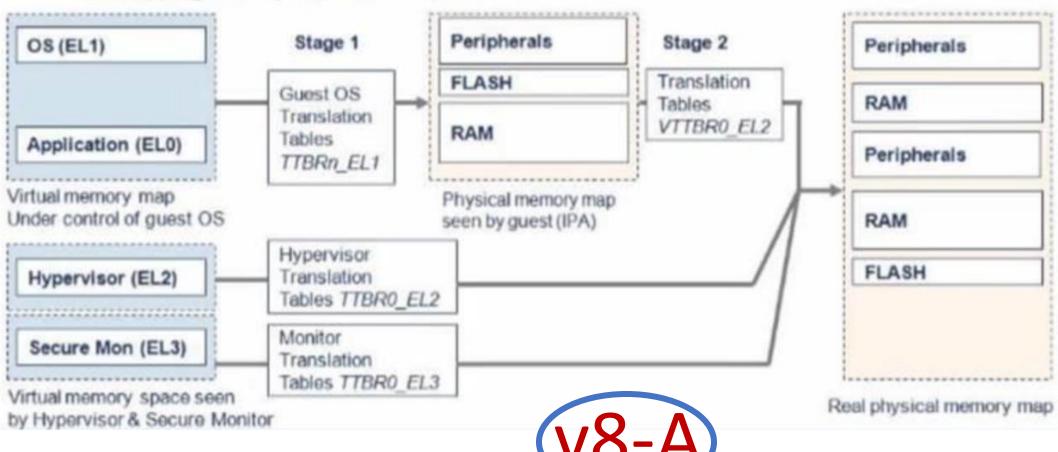

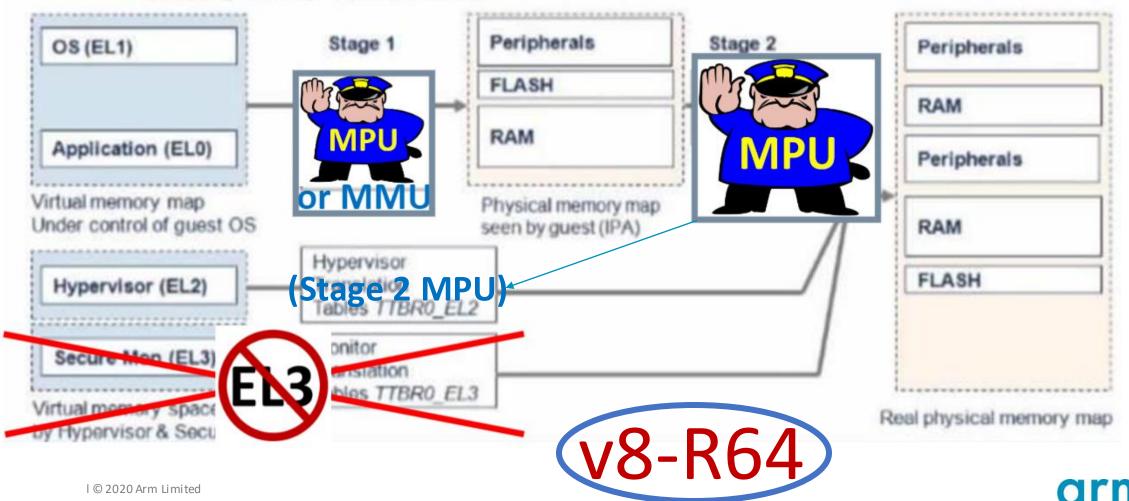

#### v8-R64 Architecture Differences – MPU

#### The Hypervisor and Secure Monitor also have a set of stage 1 Translation Tables

Mapping directly from VA to PA

#### v8-R64 Architecture Differences – MPU

The Hypervisor and Secure Monitor also have a set of stage 1 Translation Tables

Mapping directly from VA to PA

## arm

## The Assignment

I © 2020 Arm Limited

#### Why Add v8-R64 Support to v8-A Firmware?

- v8-A and v8-R64 are far more similar than different.

- Most of the trusted-firmware code for v8-A is useful for v8-R64 as well.

- If a separate trusted-firmware project were created for v8-R64, we would have a huge parallel-maintenance headache.

- SystemReady IR certification for v8-R64 cores requires compliance with EBBR, and building from the TF-A framework puts us on the path toward that goal.

Perhaps the best reason though, is that open-source software is all about pooling our efforts. Adding v8-R64 developers support would recruit even more review and development talent to Trusted Firmware!

#### The Immediate Assignment

- The immediate assignment was *not* to port all of TF-A to v8-R64.

- The immediate assignment was:

- To *port BL1 only*, to *EL2* and *MPU*,

- to adapt BL1 authenticate, opaquely load, and transfer control to a Customer/Partner run-time system instead of BL2, and

- to support Recovery-mode FWU.

#### The Immediate Assignment

# CIM

### Ramifications of v8-R64 Differences

#### **No-EL3 Ramifications**

- Although v8-R64 instruction set is essentially the same as v8-A, there are no EL3 System Registers.

- BL1 normally runs in EL3, but for v8-R64 cores it runs at EL2. We say BL1 runs in "ELmax".

- Ramifications: Any and every manipulation of EL3-specific resources is redirected to corresponding EL2-specific resources.

- In the majority of BL1-code accesses to EL3 System-Register bit fields, the same bit fields are the same for the corresponding EL2 register.

- el3\_common\_macros.S turned into el\_max\_common\_macros.S, with the macros parameterized to which EL to act upon.

- EL2 BL1 loads BL33 (runtime environment), then transfer of control.

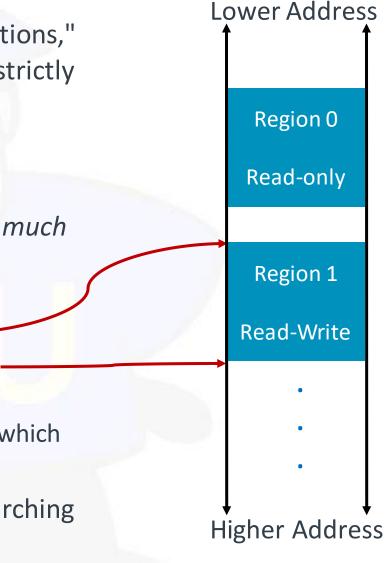

### MPU Ramifications – MPU? Wuzzat?

- Memory-Protection Units are still said to "perform translations," but don't change addresses: PA = IPA = VA. Everything is strictly flat-, direct-mapped.

- MPUs only apply permissions to specified, contiguous address *regions*.

- Most importantly, they are *register-based*, making timing *much more-deterministic* (no table walks).

- Regions are specified by System Registers:

- PRBAR\_ELn, Protection Region Base-Address Register

- PRLAR\_ELn, Protection Region Limit Address Register, also specifies permissions (which MAIR)

- **PRENR\_ELn**, Protection Region Enable Register (bitmap of which regions are enabled)

- Entirely register-based, so no non-deterministic-speed searching through page tables in memory.

#### **MPU Ramifications**

- As mention earlier, v8-R64 instruction set matches v8-A, but the System Registers do have substantial differences, for MPU support.

- Clearly, the most obvious ramification of having an MPU is that we need to add code to "drive" the MPU.

- For the immediate, short-run assignment, we only need to support the EL2/Stage-2 MPU, and not (yet) the EL1/0 Stage-1 MPU.

- MPUs also typically support far fewer regions than an MMU typically does.

- However, MPUs are more versatile in that they don't impose page-size granularity limitations.

- Overlapped MPU regions are not supported.

g

#### **No Non-Secure Ramifications**

• Having no EL3 to switch NS/Secure, v8-R64 mandates everything Secure mode.

- Arguably, making *everything* Secure makes *nothing* secure, or at least nothing any *more* secure than anything else.

- Still, this turns out to be lucky for TB-R purposes, because BL1 normally operates in Secure mode. The requested memory-translation permissions are already requested for Secure mode.

- Nevertheless, v8-R64 makes provisions for generating NS accesses from the Secure state:

- The MMU region descriptors also have an equivalent NS bit.

- We haven't seen need to use this feature, but it's available if at some point we do need it.

# arm

### The Details

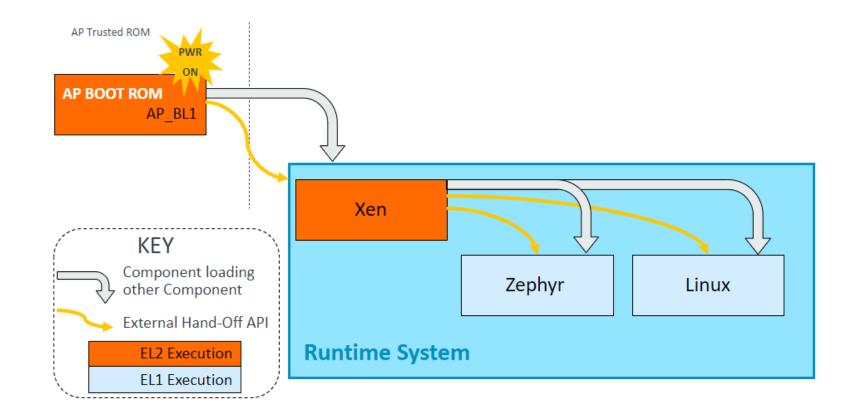

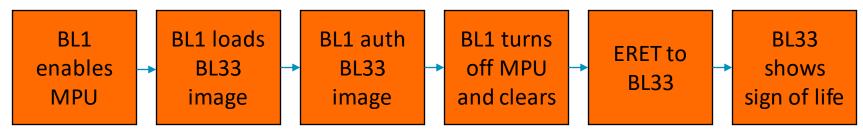

### Loading Runtime System and Transfer of Control

- Load and Transfer from BL1 to BL33:

- In EL2, BL1 enables MPU and loads and authenticates the BL33 image, which for v8-R64 purposes is the customer/partner runtime system, or bootwrapped-OS.

- TBBR support is extended to fvp\_r platform for BL1 for authentication.

- After turning off the MPU and clearing regions, then an ERET is used to jump to the base address of BL33 for execution directly from BL1.

- We used an internal bootwrapped-OS to test the transfer of control from BL1 to BL33 for a shell prompt on a UART as a sign of life.

- Transfer from BL1 to Recovery mode FWU:

- The transfer from BL1 to Recovery mode FWU remains the same as BL1 copies the image from external interfaces and updates if the image can be authenticated.

#### TB-R Memory Map change requirements

- For addresses in the 0-0xffffffff range, the v8-R64 memory map is similar with v8-A, but the upper 2GB and lower 2GB are switched.

- In other words, bit 31 is reversed, so, for example, DRAM1 is at address 0 rather than address 0x80000000.

- See <u>https://developer.arm.com/documentation/100964/1113/Base-Platform/Base---memory/Base-Platform-memory-map</u>

and <u>https://developer.arm.com/documentation/100964/1113/Base-Platform/Base---memory/BaseR-Platform-memory-map</u>

• The reasons are explained in the above documents, but for now, just FYI, the addresses are different from most other platforms.

### **Porting Approach**

- Created a new .../trusted-firmware-a/lib/xlat\_mpu library:

- API is similar, where applicable.

- For example, to program regions, you still set up a terminated array of mmap\_region\_t-type structs, and call setup\_page\_tables() to create those regions. mmap\_add\_region() still creates.

- Enable calls, however, named enable\_mpu\_\*() rather than enable\_mmu\_\*(). Same for disable\_\*().

- #define NO\_EL3 (probably change to BL1\_AT\_EL2) to divert EL3-resource accesses to EL2.

- Created the fvp\_r platform, patterned after Cortex R-82, that was ported to and tested on the v8-R64 FVP.

- BL1 image that stays in EL2 using MPU, loads the BL33 image, wipes MPU regions, and then jumps to the BL33 image.

- For our testing purposes we used an internal OS to test the transfer of control from BL1 to BL33.

#### **Review Approach**

- Gerrit reviews:

- <u>https://review.trustedfirmware.org/c/TF-A/trusted-firmware-a/+/10512</u> Platform definition

- <u>https://review.trustedfirmware.org/c/TF-A/trusted-firmware-a/+/10518</u> No-EL3 and MPU

- <u>https://review.trustedfirmware.org/c/TF-A/trusted-firmware-a/+/10519</u> Validate and load system

- <u>https://review.trustedfirmware.org/c/TF-A/trusted-firmware-a/+/10520</u> Documentation

- As with most new platforms, this is a rather large change, and it can't really be broken down much into smaller, stand-alone patches, and still compile.

- We hope to create a Phabricator site to help review *new files*:

- Most of the "new" files are not really new, but derived from existing files.

- The Gerrit review, however, has no way of knowing which existing files to compare them to.

- If successful, we'll create a table listing each new file, which of the above patches it was created under, plus an sdiff output against a close-relative existing/familiar file.

#### Resources

- <u>https://www.arm.com/products/silicon-ip-cpu/cortex-r/cortex-r82</u>

- <u>https://www.arm.com/company/news/2020/09/highest-performance-arm-cortex-r-processor</u>

- <u>https://community.arm.com/developer/tools-software/oss-platforms/w/docs/626/armv8-r-aarch64</u>

|     |     | L   | ±   | L   | L . | 4   | L   | + - |     |     |     |     |     | L. |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| r ' | T . | r · | T I | r · | T ' | T 1 | r · | T 1 | r · | r - | r · | r 1 | - 1 | Г  |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |

|  | rn | $\mathbf{n}^{+}$ |  |  | The Arm trademarks featured in this presentation are registered<br>trademarks or trademarks of Arm Limited (or its subsidiaries) in<br>the US and/or elsewhere. All rights reserved. All other marks<br>featured may be trademarks of their respective owners. |

|--|----|------------------|--|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  |    |                  |  |  |                                                                                                                                                                                                                                                                |

www.arm.com/company/policies/trademarks

|  | © 2020 Arm L | i mi ted <sup>+</sup> |  |  |  |  |  |  |

|--|--------------|-----------------------|--|--|--|--|--|--|

| <sup>†</sup> Thank You |  |  |  |  | $\mathbf{n}^{+}$ | rn | Ó |  |

|------------------------|--|--|--|--|------------------|----|---|--|

| Danke                  |  |  |  |  |                  |    | + |  |

| Merci                  |  |  |  |  |                  |    |   |  |

| 谢谢                     |  |  |  |  |                  |    |   |  |

| ありがとう                  |  |  |  |  |                  |    |   |  |

| Gracias                |  |  |  |  |                  |    |   |  |

| Kiitos                 |  |  |  |  |                  |    |   |  |

| 감사합니다                  |  |  |  |  |                  |    |   |  |

| धन्यवाद                |  |  |  |  |                  |    |   |  |

| ۺػڔٞٵ                  |  |  |  |  |                  |    |   |  |

| ধন্যবাদ                |  |  |  |  |                  |    |   |  |

| תודה                   |  |  |  |  |                  |    |   |  |

l © 2020 Arm Limited